728x90

반응형

● Hertz (헤르츠); Hz

하인리히 루돌프 헤르츠 (Heinrich Rudolph Hertz; 1857-1894)

● Oscillator 오실레이터 (보통, Hertz 라고 부른다)

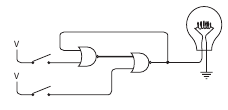

● Clock (클럭); Clk 회로의 '값보존' 대신에 '클럭'이라는 이름이 사용된다.

실제 시계가 아니라 0과 1사이를 주기적으로 왔다 갔다 하는 시계와 비슷한 속성을 지니고 있는 신호

아래 회로에서 클럭은 데이터 입력이 언제 저장되어야 하는지를 알려주는 신호라고만 생각해도 됨.

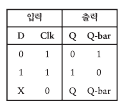

이 용어는 해당 회로가 한 비트의 데이터를 나중에 사용하기 위하 저장(latch)할 수 있다는 의미이다.

이 회로는 1-bit 메모리라고도 불림.

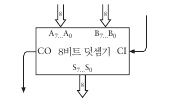

설명: 각각 8개의 A, B 입력과 B입력은 스위치에, 자리올림 입력(CI)은 접지에 연결되며,

8개의 S(sum) 입력과 자리올림 출력(CO)은 전구에 연결된다.

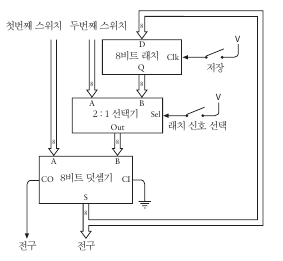

선택에 따라서 두번째 열에 있는 스위치 입력 값과 래치의 Q출력 값 중에

어떤 값이 덧셈기의 B 입력으로 들어갈지 결정할 수 있도록 해준다.

2:1 선택기 회로는 다음과 같다.

728x90

'개발자 페이지 > Code' 카테고리의 다른 글

| 아스키 코드 간단 정의 & 짧은 역사 (0) | 2022.12.03 |

|---|---|

| 반도체란? 트랜지스터의 발명 및 역사 (0) | 2022.11.09 |

| 혼자서 움직이는 컴퓨터 (0) | 2022.10.11 |

| Relay / Inverter Relay (0) | 2022.08.25 |